## 6.622 Power Electronics Assessment #2

Due: Thursday March 9, 2023 at 11:00 pm (Cambridge time)

| VAL | ID | TIA | NAT |  |

|-----|----|-----|-----|--|

| YOU | IK | NA  | VIE |  |

Solutions

## YOUR KERBEROS ID

## General Instructions:

- You must complete this assessment on your own with no consultation or discussion with any other person, excepting 6.622 staff, of whom you may ask clarifying questions. Do not discuss your solutions with anyone until the solutions have been released.

- You may use a calculator and review the course lectures, notes and textbook (Principles of Power Electronics) when completing this assessment. Please do not use other computational tools or reference materials.

- 3. Please do all of your work in the space provided. In particular, try to do your work for each question within the boundaries of the question, or on the additional pages at the end of the uploaded document, clearly marking those pages to indicate what problem they relate to. Place the answer to each question within the appropriate answer box.

- The assessment must be completed and uploaded by the indicated date/time to receive credit.

- Please make sure to show all of your work. This is important both for you

to receive credit for a correct answer and to receive partial credit when an

answer is wrong or incomplete.

## Problem 1

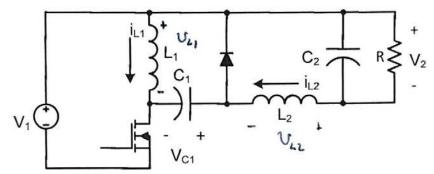

Figure 1 shows a type of PWM dc-dc converter. The switch is turned on with duty ratio D. You may assume that it operates in continuous conduction mode, and that the capacitor voltages and inductor currents have small ripple.

- a. Please find the steady-state voltage  $V_{C1}$  on capacitor  $C_1$  in terms of one or more of  $V_1$ ,  $V_2$ , and D.

- b. What is the steady-state voltage conversion ratio V<sub>2</sub>/V<sub>1</sub> of this topology as a function of switch duty ratio *D*?

- c. What polarities of voltage  $V_1$  are permissible in this particular implementation (i.e,  $V_1 > 0$  only,  $V_1 < 0$  only, or either polarity)? Why?

Figure 1 A PWM dc-dc converter.

(a) ans. KYL

$$\langle V_{C1} \rangle + \langle V_{C2} \rangle + \langle V_{2} \rangle - \langle V_{L1} \rangle = 0$$

when  $\langle V_{L1} \rangle = \langle V_{L2} \rangle = 0$

1. PSS

$$V_{C1} = -V_{2}$$

(b)

$$\langle V_{L2} \rangle = DT (V_1 - V_2 - V_{c1}) + (1-D)T(-V_2) = 0 \text{ in PSS}$$

$$\therefore DV_1 = (1-D) V_2 \Rightarrow \left| \frac{V_2}{V_1} = \frac{D}{1-D} \right|$$

(c) Because of body diede of MOSFET and LVLIZ=0, July V, >0 is allowed

Note: This is the "common-positives" version of the "Zeta" or "inverse sepic" converter

(a)

$$V_{C1} = -V_{2}$$

or  $-\frac{D}{1-D}V_{1}$

(b)  $V_{2}/V_{1} = \frac{D}{1-D}$

(b)

$$V_2/V_1 = \frac{D}{1-D}$$

circle one:  $V_1 > 0$  only  $V_1 < 0$  only either polarity Explanation: (c)

Power moefet can only support +ve VI

MIT OpenCourseWare <a href="https://ocw.mit.edu">https://ocw.mit.edu</a>

6.622 Power Electronics Spring 2023

For information about citing these materials or our Terms of Use, visit: <a href="https://ocw.mit.edu/terms">https://ocw.mit.edu/terms</a>