### VLIW/EPIC: Statically Scheduled ILP

### Joel Emer

Computer Science & Artificial Intelligence Laboratory Massachusetts Institute of Technology

> Based on the material prepared by Krste Asanovic and Arvind

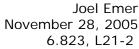

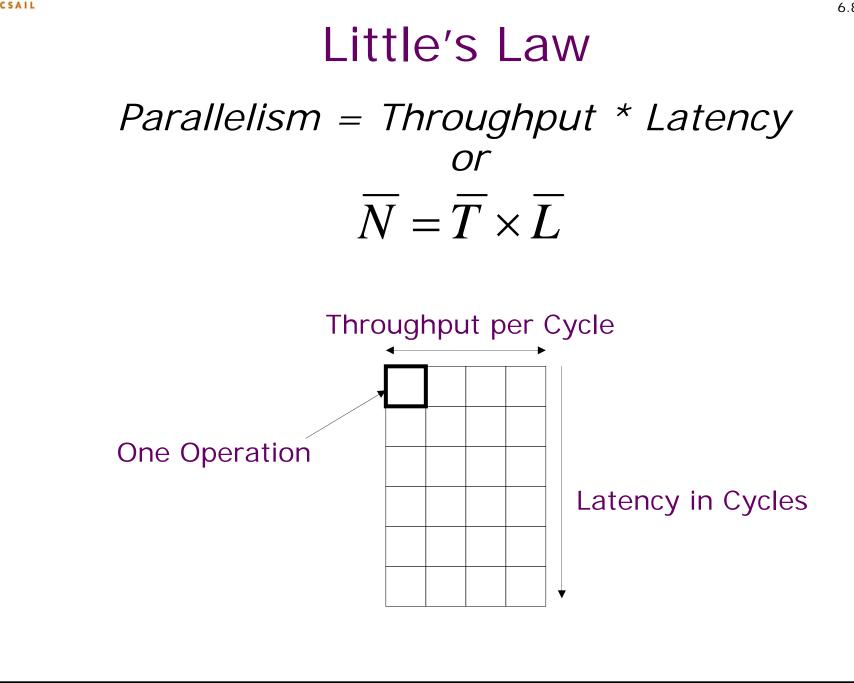

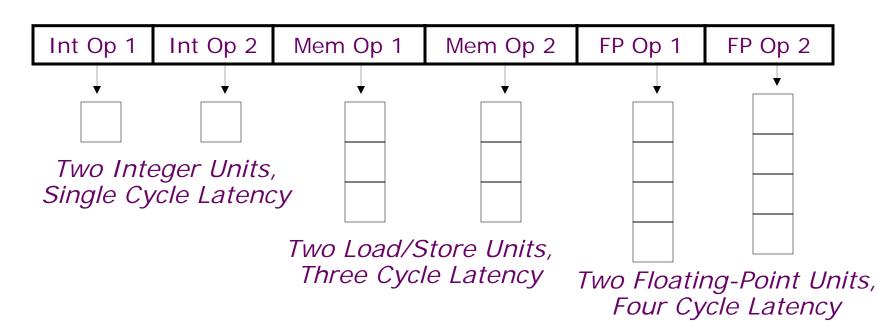

• How much instruction-level parallelism (ILP) required to keep machine pipelines busy?

$$\overline{T} = 6 \qquad \overline{L} = \frac{(2x1 + 2x3 + 2x4)}{6} = 2\frac{2}{3} \qquad \overline{N} = 6 \times 2\frac{2}{3} = 16$$

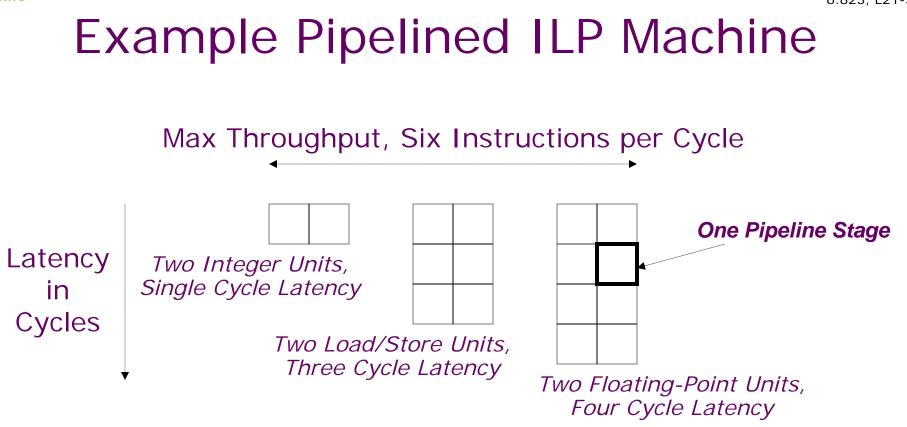

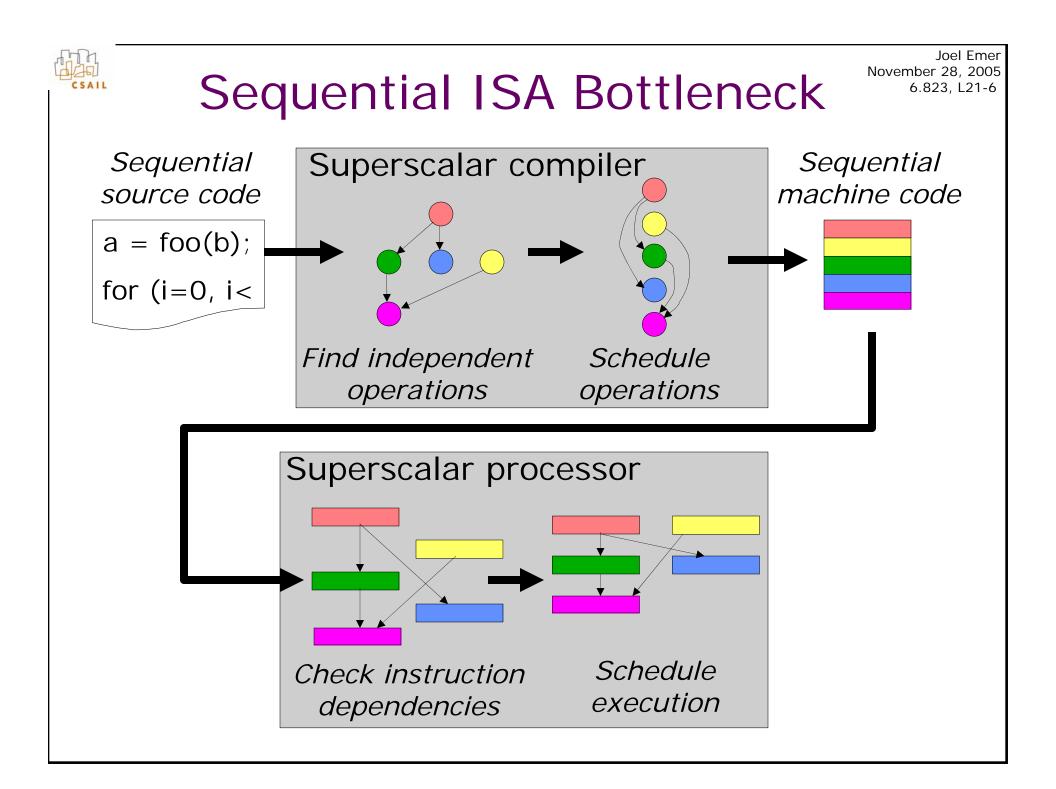

# Superscalar Control Logic Scaling

- Each issued instructions must make interlock checks against W\*L instructions, i.e., growth in interlocks  $\propto$  W\*(W\*L)

- For in-order machines, L is related to pipeline latencies

- For out-of-order machines, L also includes time spent in instruction buffers (instruction window or ROB)

- As W increases, larger instruction window is needed to find enough parallelism to keep machine busy => greater L

=> Out-of-order control logic grows faster than  $W^2$  (~ $W^3$ )

CSAIL

Joel Emer November 28, 2005 6.823, L21-5

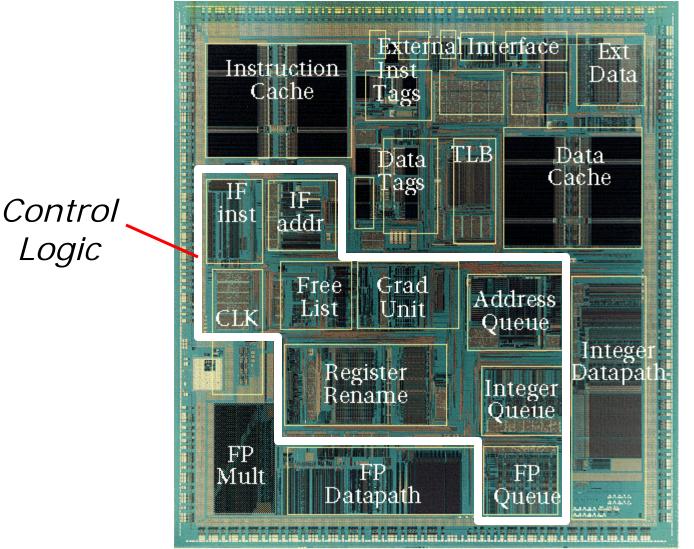

### Out-of-Order Control Complexity<sup>6,82</sup> MIPS R10000

[ SGI/MIPS Technologies Inc., 1995 ]

### **VLIW: Very Long Instruction Word**

- Multiple operations packed into one instruction

- Each operation slot is for a fixed function

- Constant operation latencies are specified

- Architecture requires guarantee of:

- Parallelism within an instruction => no x-operation RAW check

- No data use before data ready => no data interlocks

# **VLIW Compiler Responsibilities**

### The compiler:

- Schedules to maximize parallel execution

- Guarantees intra-instruction parallelism

- Schedules to avoid data hazards (no interlocks)

Typically separates operations with explicit NOPs

## Early VLIW Machines

- FPS AP120B (1976)

- scientific attached array processor

- first commercial wide instruction machine

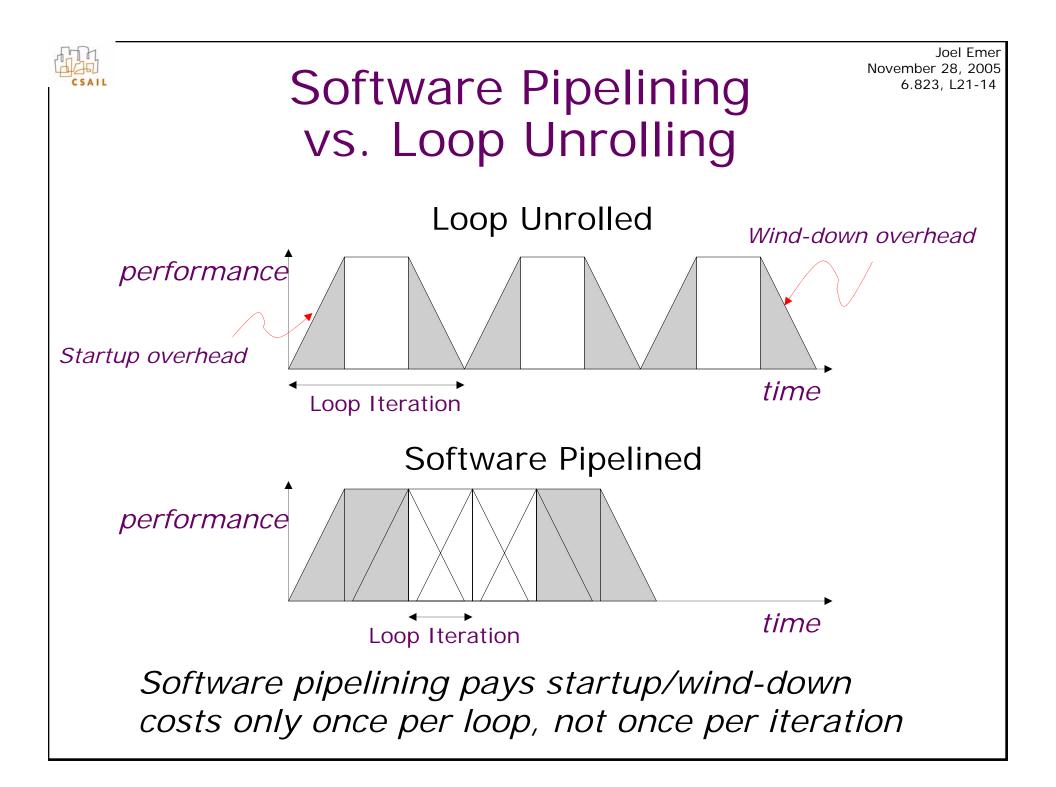

- hand-coded vector math libraries using software pipelining and loop unrolling

#### • Multiflow Trace (1987)

- commercialization of ideas from Fisher's Yale group including "trace scheduling"

- available in configurations with 7, 14, or 28 operations/instruction

- 28 operations packed into a 1024-bit instruction word

- Cydrome Cydra-5 (1987)

- 7 operations encoded in 256-bit instruction word

- rotating register file

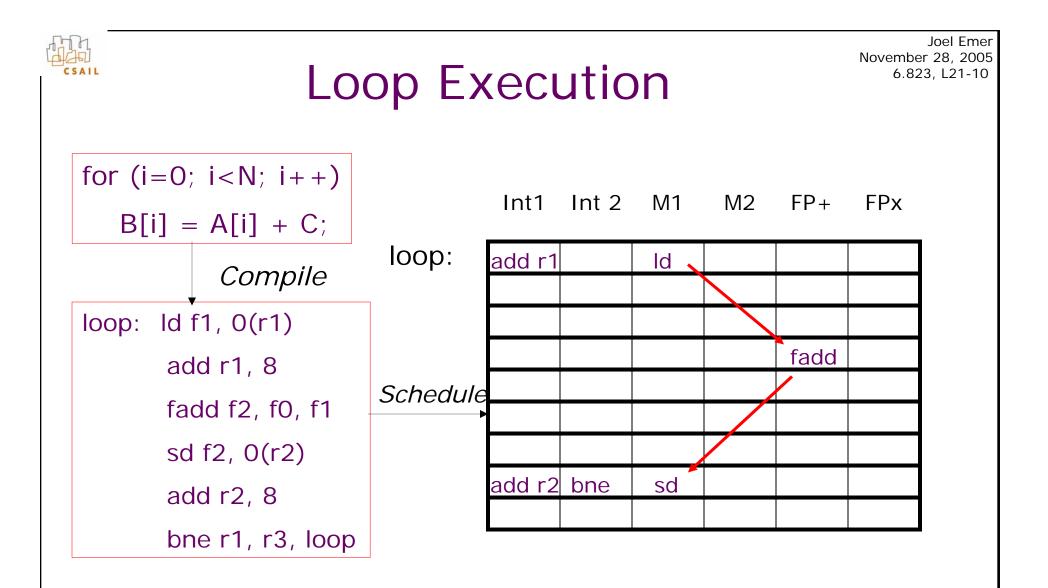

How many FP ops/cycle?

1 fadd / 8 cycles = 0.125

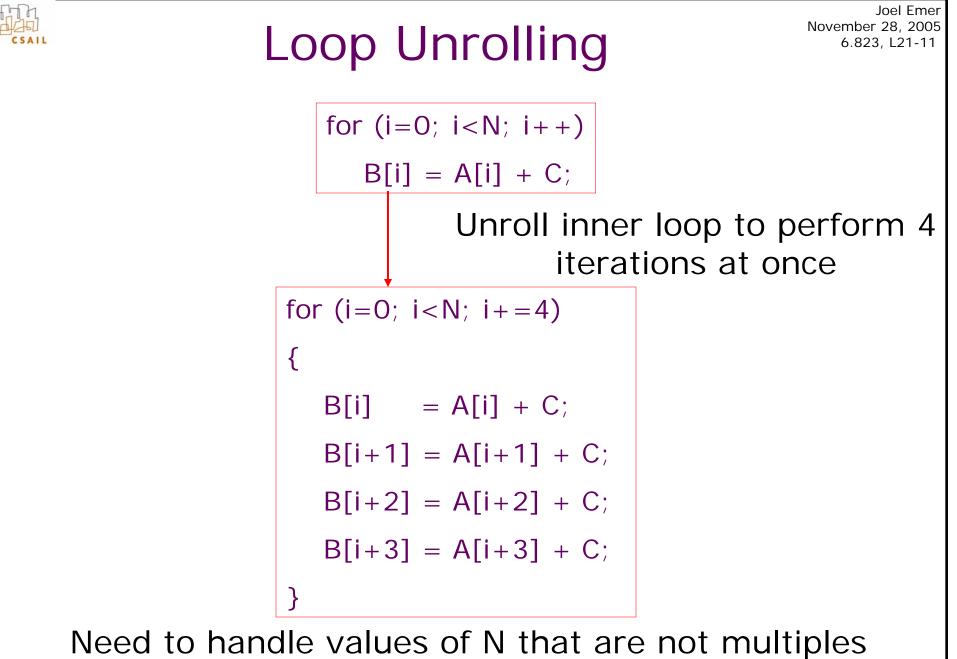

of unrolling factor with final cleanup loop

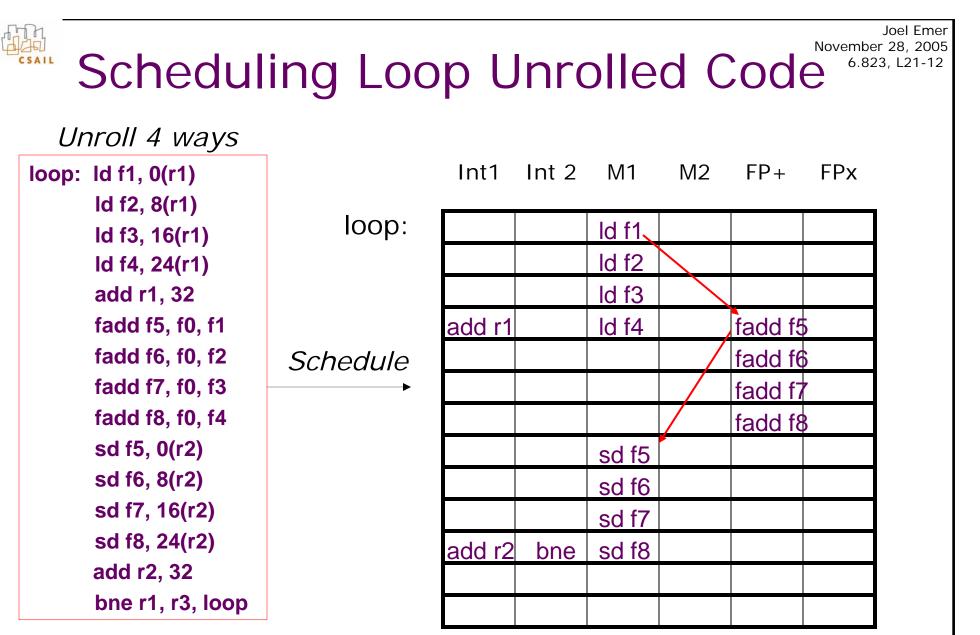

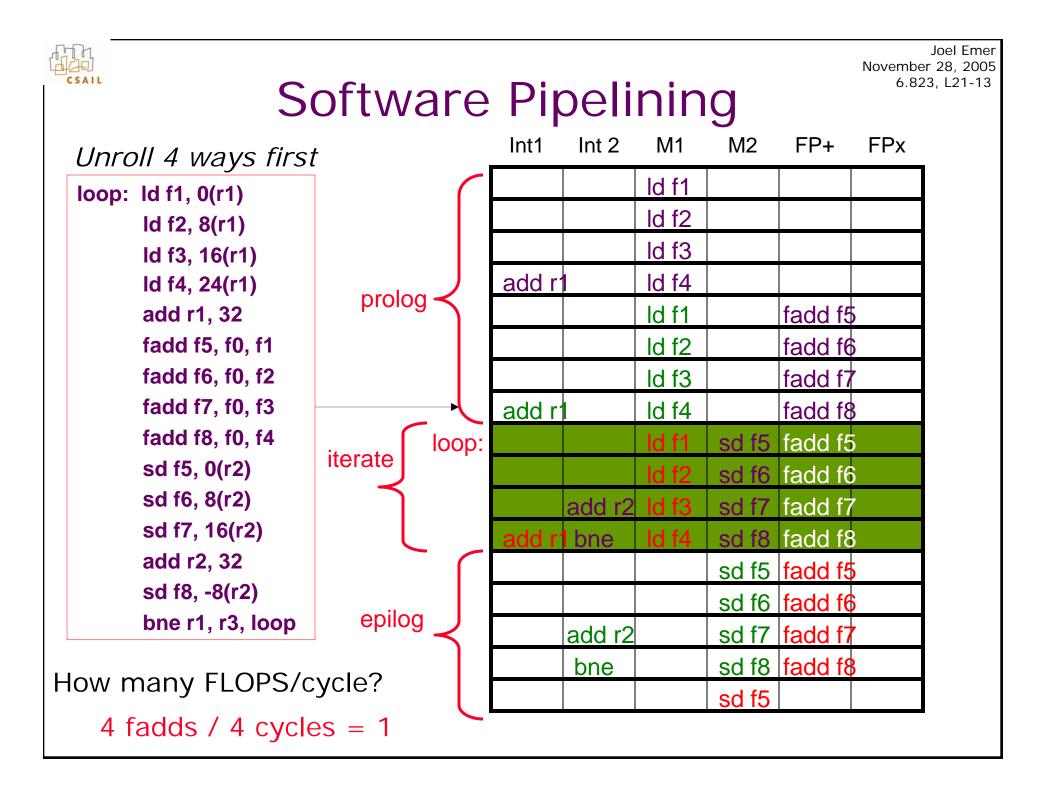

How many FLOPS/cycle?

4 fadds / 11 cycles = 0.36

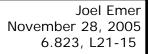

- Branches limit basic block size in control-flow intensive irregular code

- Difficult to find ILP in individual basic blocks

### Trace Scheduling [Fisher, Ellis]

- Pick string of basic blocks, a *trace*, that represents most frequent branch path

- Use <u>profiling feedback</u> or compiler heuristics to find common branch paths

- Schedule whole "trace" at once

- Add fixup code to cope with branches jumping out of trace

## Problems with "Classic" VLIW

- Object-code compatibility

- have to recompile all code for every machine, even for two machines in same generation

- Object code size

- instruction padding wastes instruction memory/cache

- loop unrolling/software pipelining replicates code

- Scheduling variable latency memory operations

- caches and/or memory bank conflicts impose statically unpredictable variability

- Knowing branch probabilities

- Profiling requires an significant extra step in build process

- Scheduling for statically unpredictable branches

- optimal schedule varies with branch path

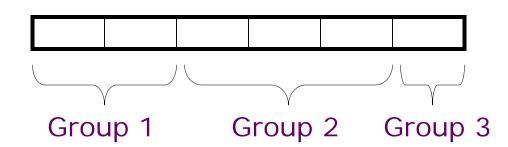

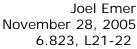

# **VLIW Instruction Encoding**

Schemes to reduce effect of unused fields

- Compressed format in memory, expand on I-cache refill

- » used in Multiflow Trace

- » introduces instruction addressing challenge

- Mark parallel groups

- » used in TMS320C6x DSPs, Intel IA-64

- Provide a single-op VLIW instruction

- » Cydra-5 UniOp instructions

Joel Emer November 28, 2005 6.823, L21-19

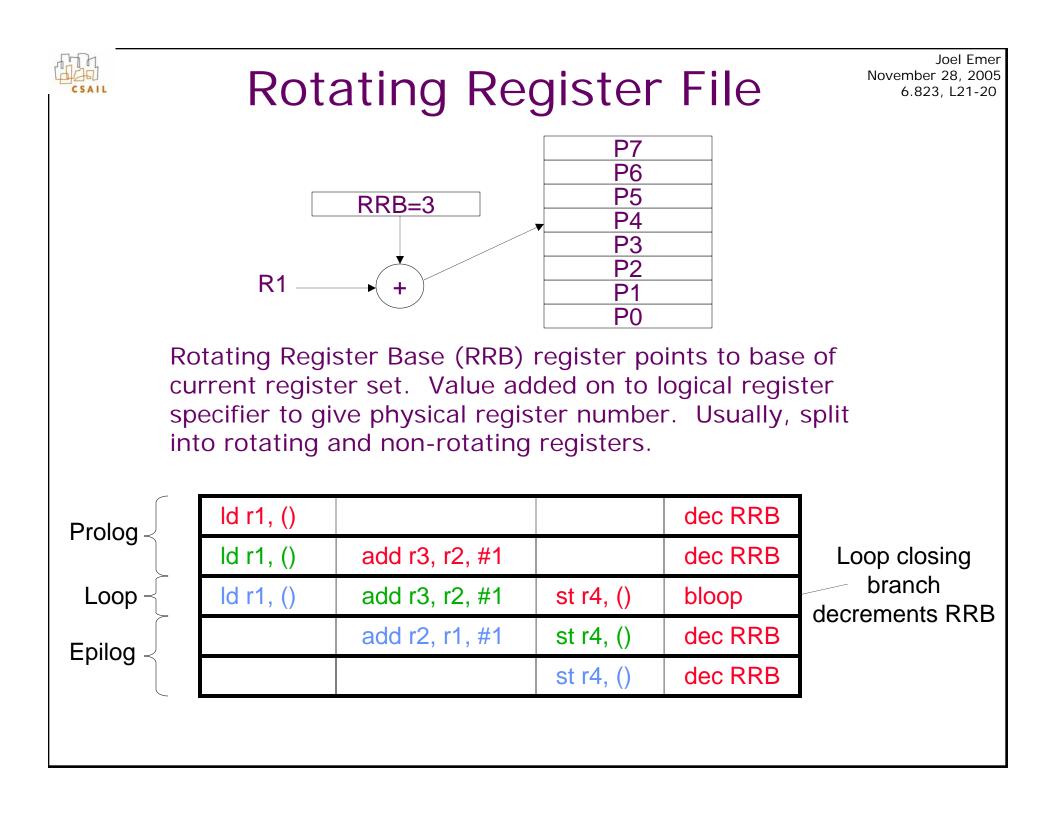

# **Rotating Register Files**

Problems: Scheduled loops require lots of registers, Lots of duplicated code in prolog, epilog

|         | ld r1, ()      |                |                |

|---------|----------------|----------------|----------------|

|         | add r2, r1, #1 | ld r1, ()      |                |

|         | st r2, ()      | add r2, r1, #1 | ld r1, ()      |

|         |                | st r2, ()      | add r2, r1, #1 |

|         |                |                | st r2, ()      |

| C       |                |                | T              |

| olog    | ld r1, ()      |                |                |

|         | ld r1, ()      | add r2, r1, #1 |                |

| oop     | ld r1, ()      | add r2, r1, #1 | st r2, ()      |

| oilog < |                | add r2, r1, #1 | st r2, ()      |

|         |                |                | st r2, ()      |

Solution: Allocate new set of registers for each loop iteration

| CSAIL | <b>Rotating Register File</b><br>(Previous Loop Example)                                                |                |                                                                                                        |       |       |  |  |

|-------|---------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------|-------|-------|--|--|

|       | Three cycle load latency<br>encoded as difference of 3<br>in register specifier<br>number (f4 - f1 = 3) |                | Four cycle fadd latency<br>encoded as difference of 4<br>in register specifier<br>number (f9 – f5 = 4) |       |       |  |  |

|       | ld f1, ()                                                                                               | fadd f5, f4,   | sd f9, ()                                                                                              | bloop |       |  |  |

|       |                                                                                                         |                |                                                                                                        | ]     |       |  |  |

|       | ld P9, ()                                                                                               | fadd P13, P12, | sd P17, ()                                                                                             | bloop | RRB=8 |  |  |

|       | ld P8, ()                                                                                               | fadd P12, P11, | sd P16, ()                                                                                             | bloop | RRB=7 |  |  |

|       | ld P7, ()                                                                                               | fadd P11, P10, | sd P15, ()                                                                                             | bloop | RRB=6 |  |  |

|       | ld P6, ()                                                                                               | fadd P10, P9,  | sd P14, ()                                                                                             | bloop | RRB=5 |  |  |

|       | ld P5, ()                                                                                               | fadd P9, P8,   | sd P13, ()                                                                                             | bloop | RRB=4 |  |  |

|       | ld P4, ()                                                                                               | fadd P8, P7,   | sd P12, ()                                                                                             | bloop | RRB=3 |  |  |

|       | ld P3, ()                                                                                               | fadd P7, P6,   | sd P11, ()                                                                                             | bloop | RRB=2 |  |  |

|       | ld P2, ()                                                                                               | fadd P6, P5,   | sd P10, ()                                                                                             | bloop | RRB=1 |  |  |

### Cydra-5: Memory Latency Register (MLR)

Problem: Loads have variable latency Solution: Let software choose desired memory latency

- Compiler schedules code for maximum load-use distance

- Software sets MLR to latency that matches code schedule

- Hardware ensures that loads take exactly MLR cycles to return values into processor pipeline

- Hardware buffers loads that return early

- Hardware stalls processor if loads return late

Joel Emer November 28, 2005 6.823, L21-23

#### Five-minute break to stretch your legs

## Intel EPIC IA-64

- EPIC is the style of architecture (cf. CISC, RISC) – Explicitly Parallel Instruction Computing

- IA-64 is Intel's chosen ISA (cf. x86, MIPS)

- IA-64 = Intel Architecture 64-bit

- An object-code compatible VLIW

- Itanium (aka Merced) is first implementation (cf. 8086)

- First customer shipment expected 1997 (actually 2001)

- McKinley, second implementation shipped in 2002

Joel Emer November 28, 2005 6.823, L21-26

### IA-64 Registers

- 128 General Purpose 64-bit Integer Registers

- 128 General Purpose 64/80-bit Floating Point Registers

- 64 1-bit Predicate Registers

- GPRs rotate to reduce code size for software pipelined loops

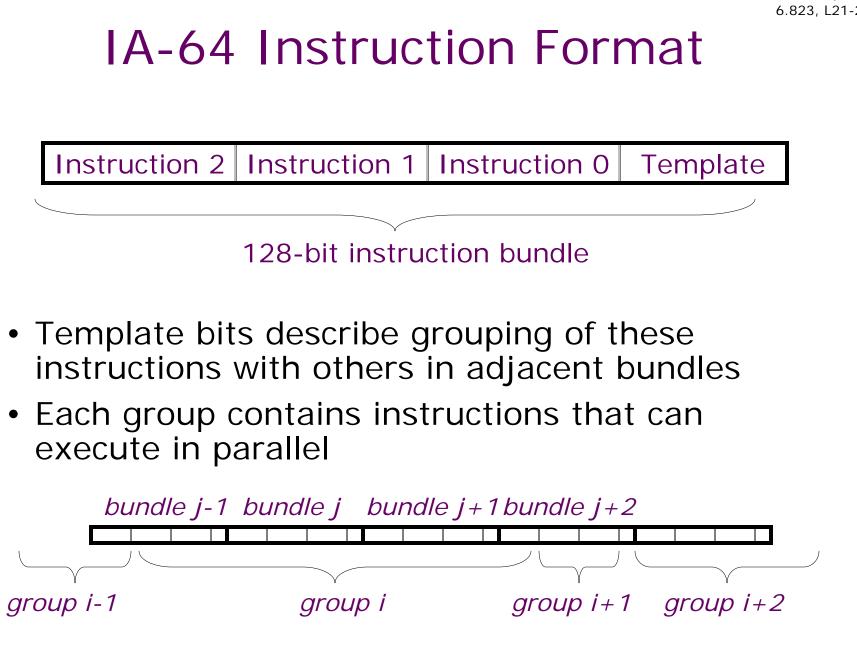

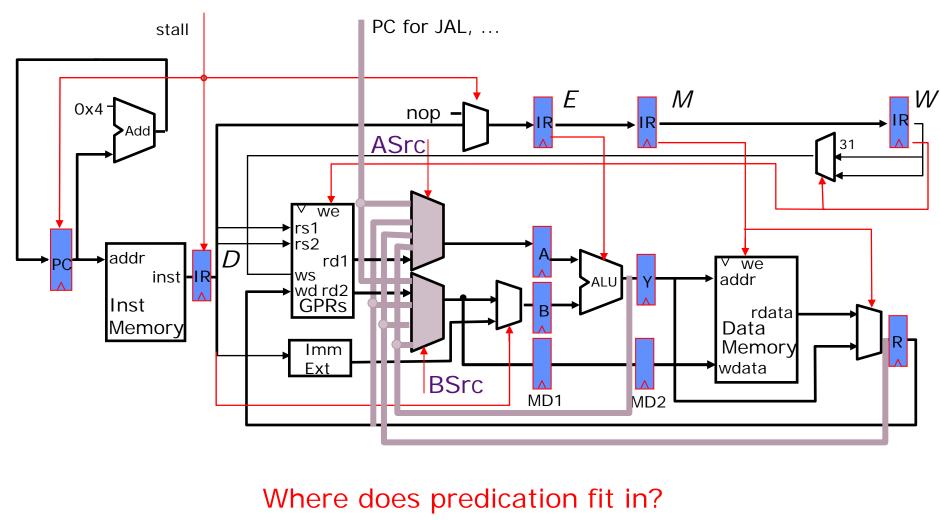

## IA-64 Predicated Execution

Problem: Mispredicted branches limit ILP

Solution: Eliminate hard to predict branches with predicated execution

- Almost all IA-64 instructions can be executed conditionally under predicate

- Instruction becomes NOP if predicate register false

## Predicate Software Pipeline Stages

Single VLIW Instruction

| (p1) ld r1        | (p2) add r3   | (p3) st r4 | (p1) bloop |  |  |  |  |

|-------------------|---------------|------------|------------|--|--|--|--|

| Dynamic Execution |               |            |            |  |  |  |  |

| (p1) ld r         | 1             | _          | (p1) bloop |  |  |  |  |

| (p1) ld r         | 1 (p2) add r3 |            | (p1) bloop |  |  |  |  |

| (p1) ld r         | 1 (p2) add r3 | (p3) st r4 | (p1) bloop |  |  |  |  |

| (p1) ld r         | 1 (p2) add r3 | (p3) st r4 | (p1) bloop |  |  |  |  |

| (p1) ld r         | 1 (p2) add r3 | (p3) st r4 | (p1) bloop |  |  |  |  |

|                   | (p2) add r3   | (p3) st r4 | (p1) bloop |  |  |  |  |

|                   |               | (p3) st r4 | (p1) bloop |  |  |  |  |

Software pipeline stages turned on by rotating predicate registers → Much denser encoding of loops

### Fully Bypassed Datapath

Joel Emer

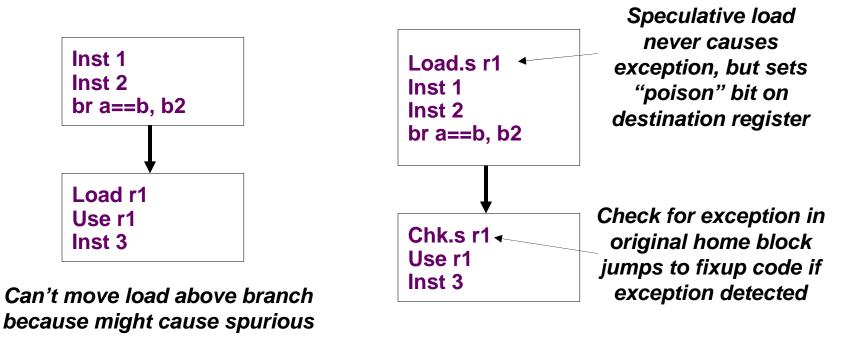

Problem: Branches restrict compiler code motion

Solution: Speculative operations that don't cause exceptions

Particularly useful for scheduling long latency loads early

exception

Joel Emer

November 28, 2005

6.823, L21-31

Problem: Possible memory hazards limit code scheduling Solution: Hardware to check pointer hazards

Requires associative hardware in address check table

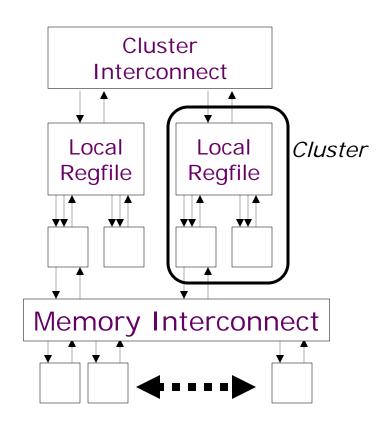

# Clustered VLIW

Cache/Memory Banks

- Divide machine into clusters of local register files and local functional units

- Lower bandwidth/higher latency interconnect between clusters

- Software responsible for mapping computations to minimize communication overhead

- Exists in some superscalar processors, .e.g., Alpha 21264

- Common in commercial embedded processors, examples include TI C6x series DSPs, and HP Lx processor

# Limits of Static Scheduling

- Unpredictable branches

- Variable memory latency (unpredictable cache misses)

- Code size explosion

- Compiler complexity

### Question:

How applicable are the VLIW-inspired techniques to traditional RISC/CISC processor architectures?

Joel Emer November 28, 2005 6.823, L21-34

### Thank you !