The World Leader in High-Performance Signal Processing Solutions

# **RF Power Amplifiers**

May 7, 2003

#### Outline

~~

RFÅ IF

#### PA Introduction

- Power transfer characteristics

- Intrinsic PA metrics

- Linear and Non-linear amplifiers

- PA Architectures

- Single-Stage Linear PA

- Load-line theory

- Transistors size

- Input and Output Matching

- So why is this so hard?

- High-efficiency PAs

- Class A, AB, B and C amplifiers

## **Outline (cont.)**

#### Real-World Design Example

- Selecting architecture, number of stages

- Designing stages

- Tuning: inter-stage match and output

#### System specifications

- Ruggedness: load mis-match and VSWR

- Linearity: spectral mask (ACPR), switching transients

- Noise in receive band

#### Power Control

RFÅ IF

# **PA Transfer characteristics**

# **Defining linearity:**

RFAIF

# **PA Transfer characteristics**

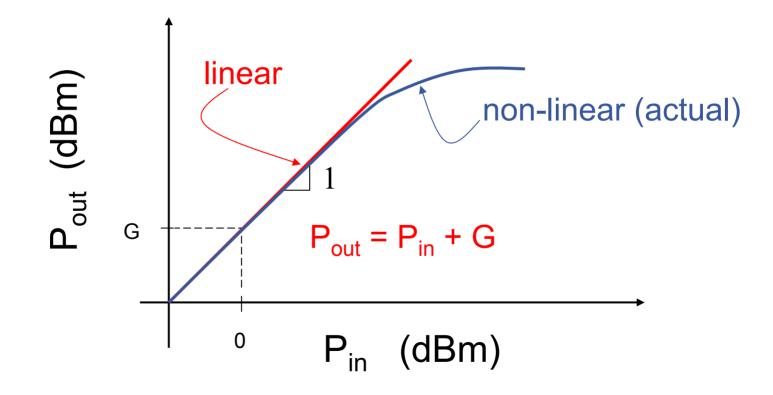

## **Defining linearity:**

RFAIF

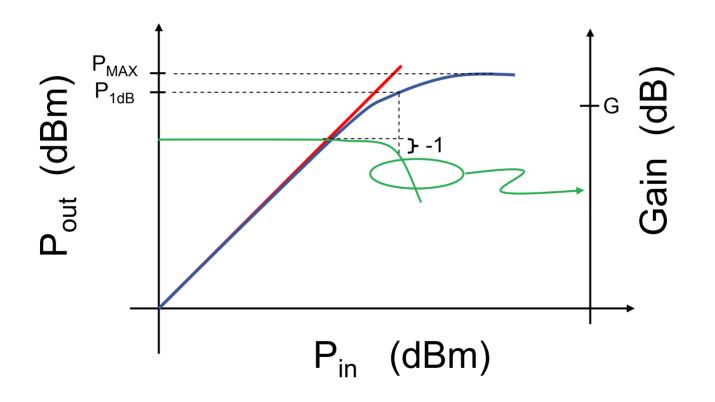

#### **PA Introduction: Intrinsic PA Metrics**

- P<sub>1dB</sub>: Output power at which linear gain has compressed by 1dB (measure of linear power handling)

- P<sub>MAX</sub>: Maximum output power (saturated power)

- Gain: Generally taken to mean transducer gain

Power delivered to load

Power available from source

• PAE: Power-added Efficiency

Power to load – Power from source

Power from supply

## **Linear and Non-linear PAs**

"Linear PA" generally refers to a PA which operates at constant gain, needs to preserve amplitude information

- Not necessarily class A (will discuss later ...) Peak efficiencies often only 40 to 45 %

- Useful for modulation schemes with amplitude modulation (QPSK, 8-PSK, QAM)

RFA IF

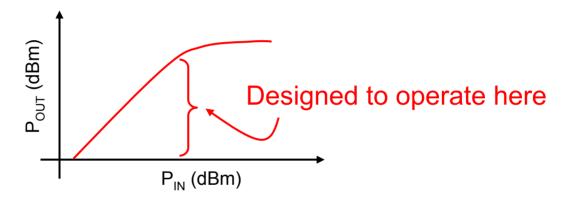

# **Linear and Non-linear PAs**

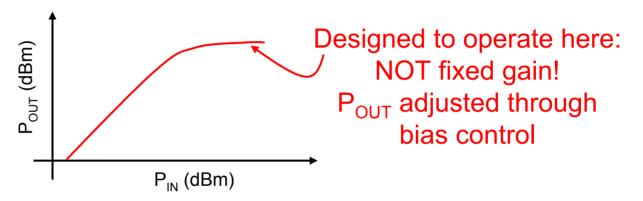

"Non-linear PA" generally refers to a PA designed to operate with constant P<sub>IN</sub>, output power varies by changing gain

Operation in saturated mode leads to high peak efficiencies

> 50%; "backed-off" efficiencies drop quickly

Useful for constant-envelope modulation schemes (GMSK)

RFA IF

RF

RFAIF

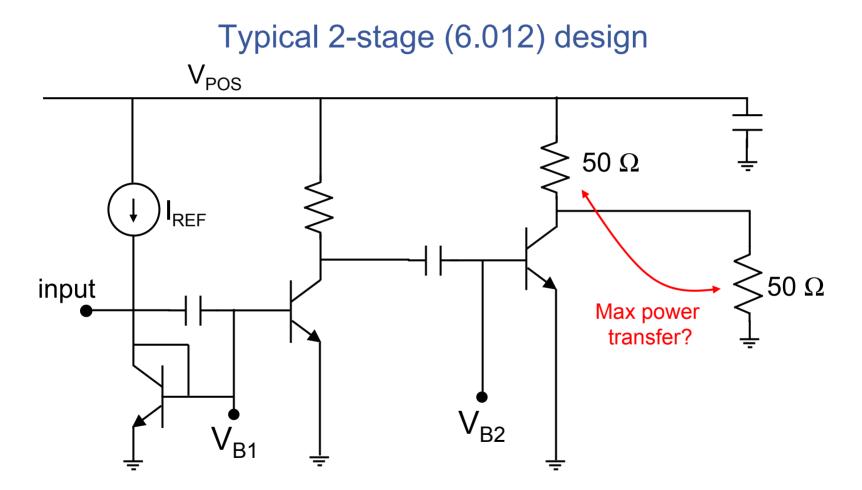

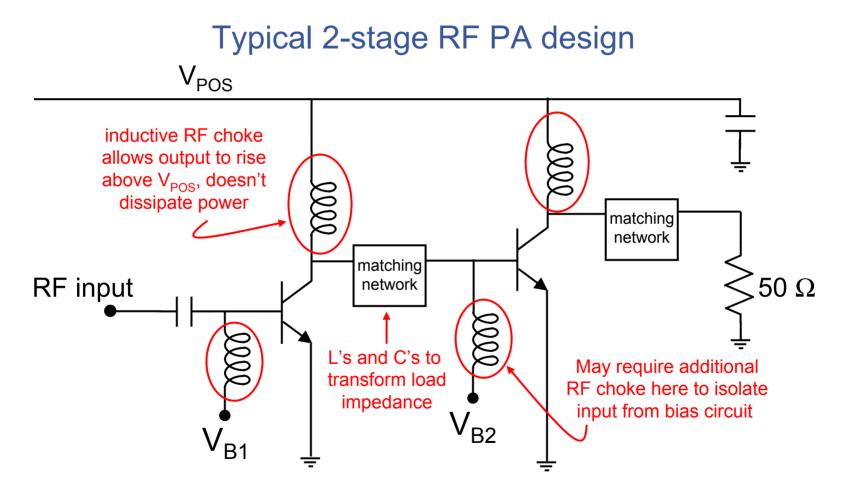

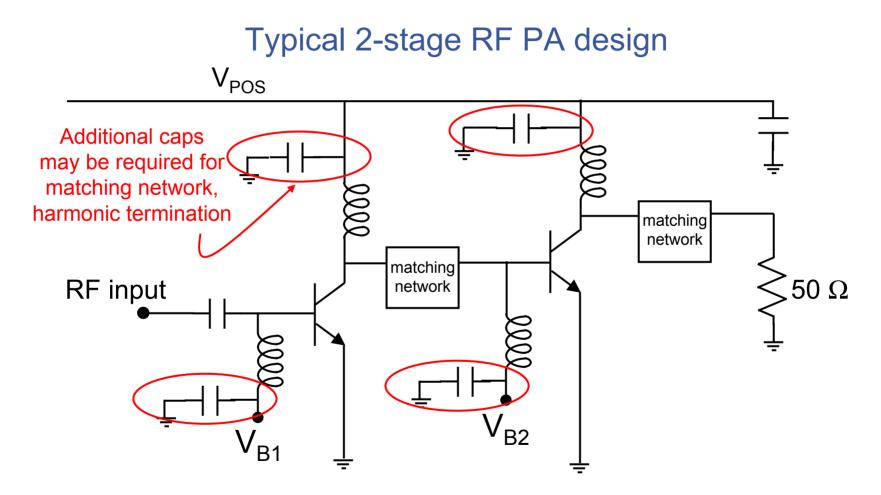

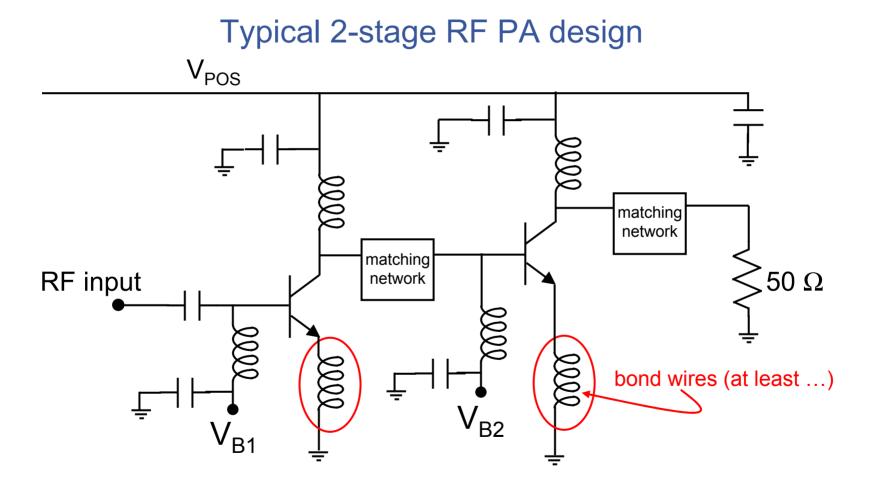

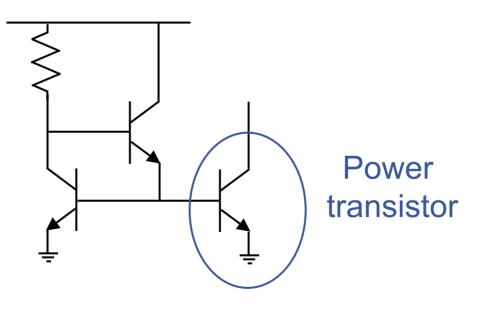

- "Gain stage" is one transistor with passive elements

- "Active" components often limited to 2 or 3 transistors (gain stages) in signal path

- Transistor design very important!

- Many parallel transistors often look like mini-circuits themselves

- Passive components just as important as transistors!

- Circuits must be tunable to account for uncertainties in determining values a priori (i.e. simulations stink – especially large-signal, RF simulations)

- Q and parasitic elements of passives important

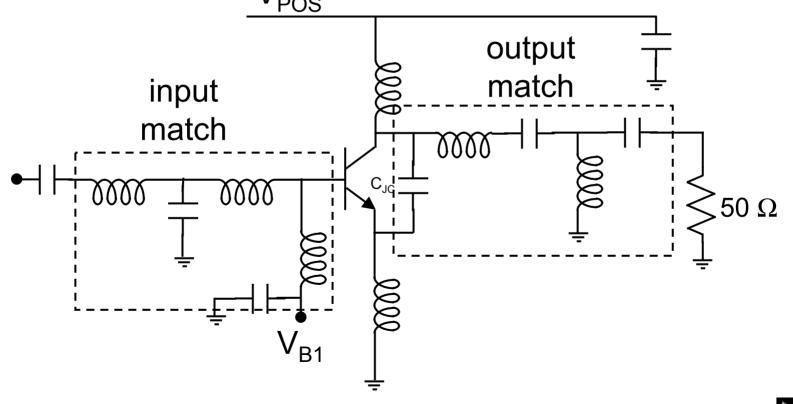

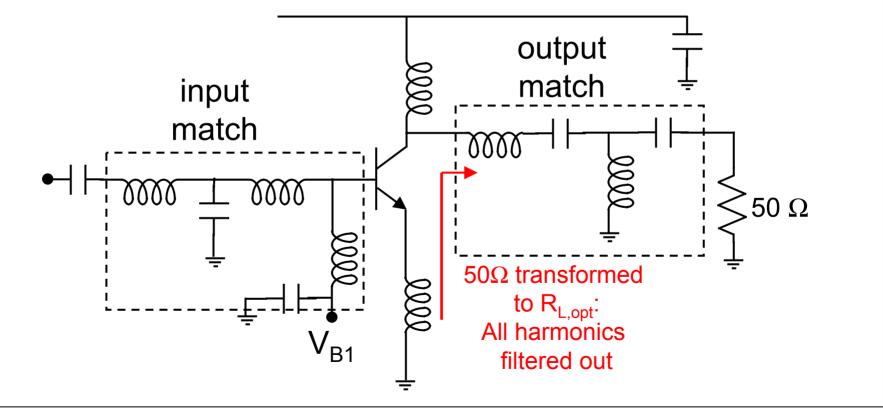

#### **Single-Stage Linear PA**

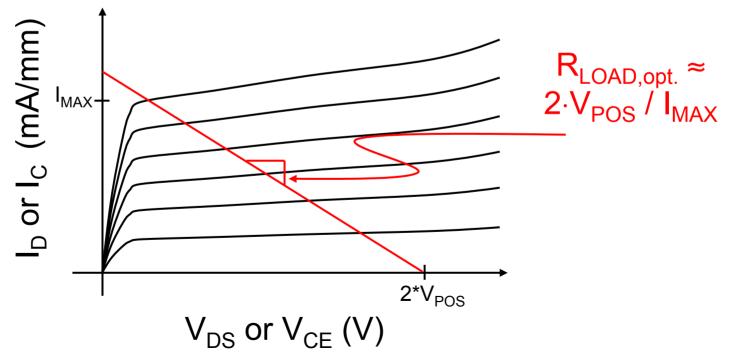

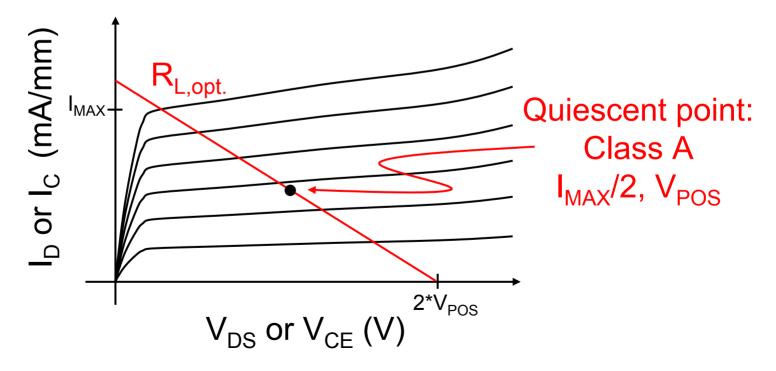

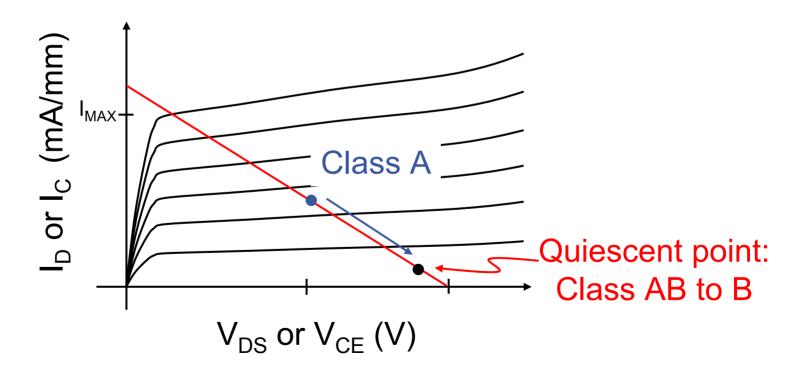

Load-line theory: the maximum power that a given transistor can deliver is determined by the power supply voltage and the maximum current of the transistor

#### **Single-Stage Linear PA**

Transistor size chosen to deliver required output power

$$P_{OUT} \approx I_{MAX} \cdot V_{POS} / 4$$

#### **Single-Stage, Linear PA**

Design output match to transform 50Ω load to R<sub>L,opt</sub> at transistor output; then design input match for gain (complex conjugate)

V<sub>POS</sub>

#### Seems simple, so why is this so hard?

#### Determining I<sub>MAX</sub> is not so easy

- For BJTs, one reference suggested that "the best way of estimating its value is to build an optimized class A amplifier and observe the dc supply current."<sup>1</sup>

- Somewhat easier for depletion-mode GaAs FETs I<sub>MAX</sub> often corresponds to V<sub>GS</sub> = 0V

- Values don't scale linearly with transistor size

- Optimal load resistance only a theoretical number

- Transmission line effects, parasitic L's and C's significant at RF

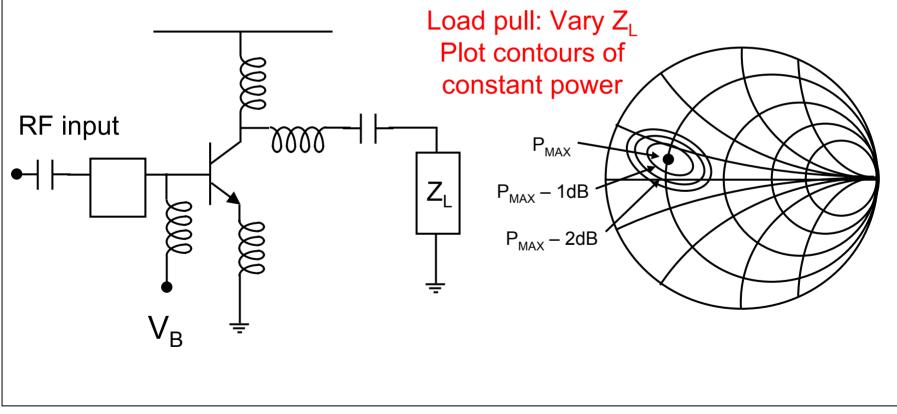

- Common practice is to vary the load of an actual transistor to determine the peak output power: the load-pull measurement (Noticing a distinct pattern of "empirical" design emerging?)

<sup>1</sup> RF Power Amplifiers for Wireless Communications, Steve Cripps, Artech House, Boston, 1999.

5

RF IF

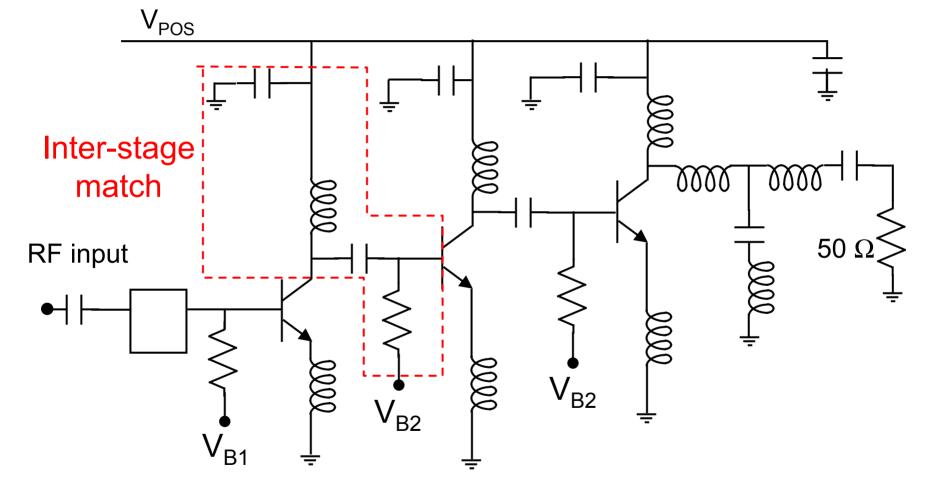

## Seems simple, so why is this so hard?

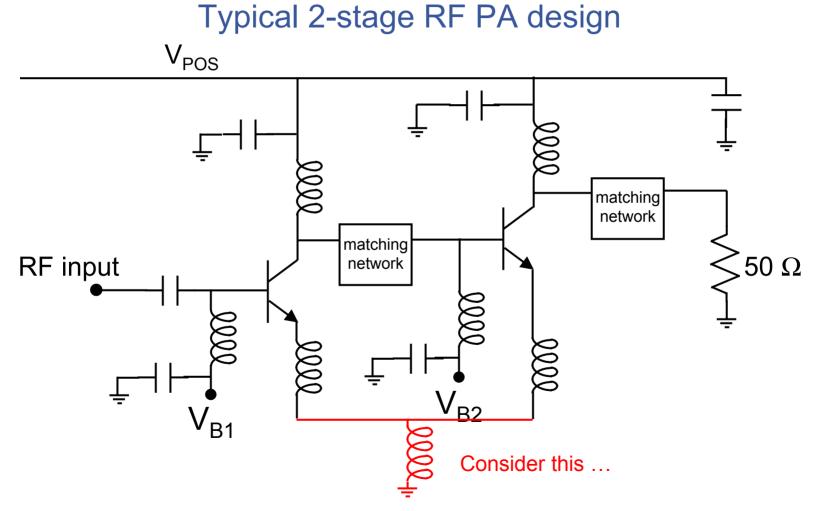

- Now consider the problem for multiple stages ... double the trouble

- Typical single-stage gain only 10 15 dB

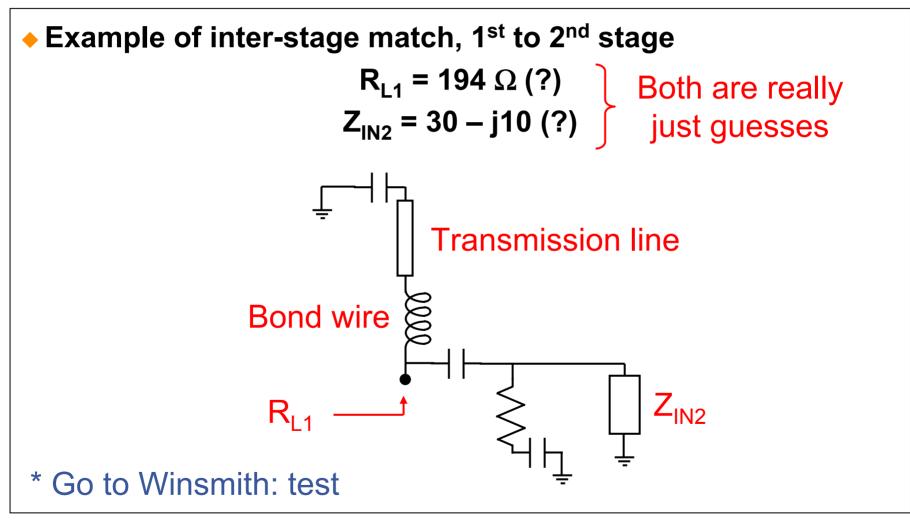

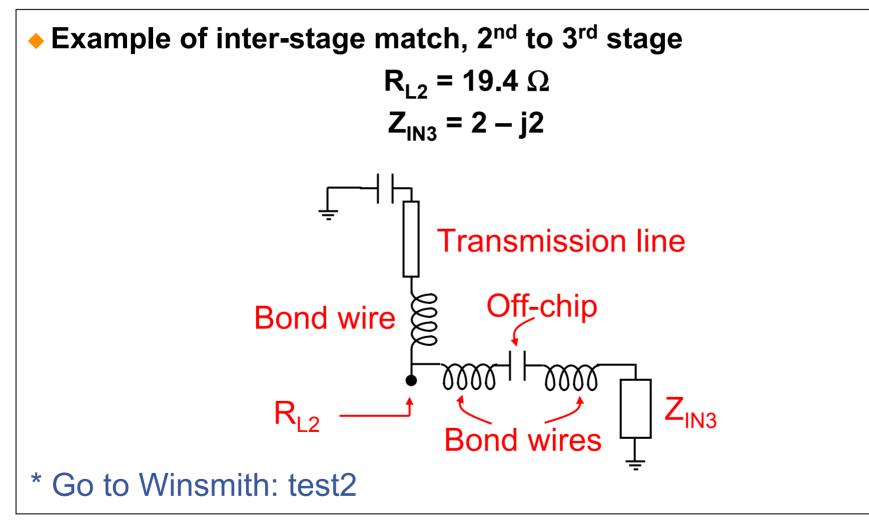

- Inter-stage match now required to match input impedance of 2<sup>nd</sup> stage to desired output impedance of 1<sup>st</sup> stage.

- Problems with matching circuits:

- Large matching ratios  $\rightarrow$  high Q circuits for simple L matches

- Multi-segment matches use valuable real estate, add cost

- Transistor itself maters a lot!

- Many parallel transistor

- Ballasting, balancing and layout extremely important

my have

RFÅ IF

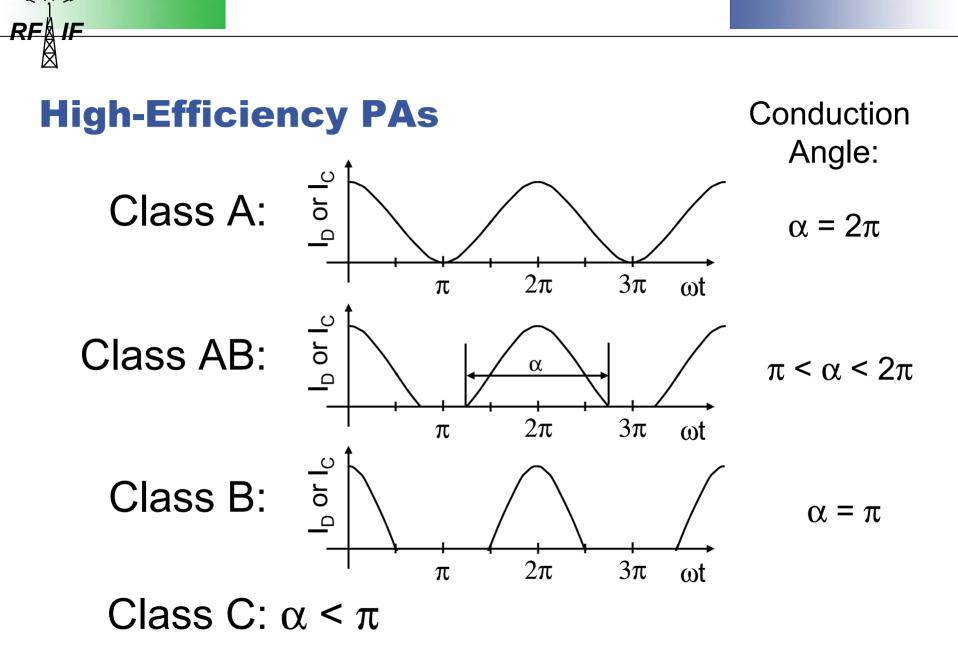

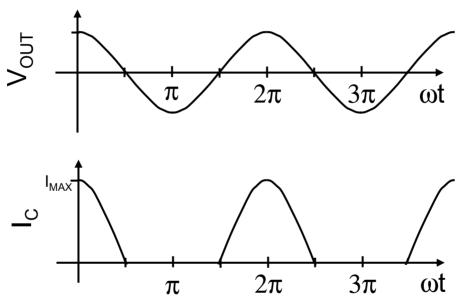

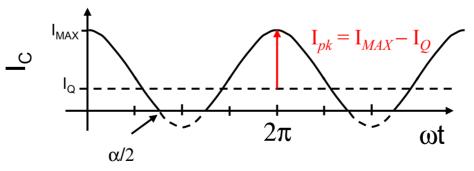

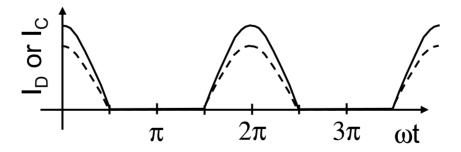

Input signal swing turns on transistor – conduction for only part of sinusoidal period

Assume output match will filter out non-linearities caused by discontinuous conduction:

If all harmonics filtered out, then voltage output at load is a pure sinusoid, despite discontinuous conduction

Energy stored in reactive elements delivers current to the load during transistor off-portion of cycle

#### Now consider peak efficiencies

**Calculate fundamental component of current**\*

$$I_{dc} = (1/2\pi) \int_{-\alpha/2}^{\alpha/2} I_{Q} + I_{pk} \cos(\omega t) \, d\omega t$$

$$I_{n} = (1/\pi) \int_{-\alpha/2}^{\alpha/2} I_{pk} \cos(\omega t) \cos(n\omega t) \, d\omega t$$

\* There are many texts which cover reduced-conduction angle calculations. See for example *Principles Of Power Electronics,* Kassakian, Schelcht and Verghese, Ch. 3.

From phasor plot:  $\cos(\alpha/2) = -I_Q / I_{pk} = -I_Q / (I_{MAX} - I_Q)$ Put it all together and do the math, you get:

$$I_{dc} = \frac{I_{MAX}}{2\pi} \frac{2\sin(\alpha/2) - \alpha\cos(\alpha/2)}{1 - \cos(\alpha/2)}$$

$$I_{1,0-p} = \frac{I_{MAX}}{2\pi} \frac{\alpha - \sin\alpha}{1 - \cos(\alpha/2)}$$

Assume  $V_{OUT}$  the same for all classes:

$$\mathbf{V}_{1,0\text{-}p} = \mathbf{V}_{\text{POS}}$$

Summary of PA "ideal" peak efficiencies

Class A:

$$\frac{P_{1}}{P_{dc}} = \frac{(I_{MAX}/2)/\sqrt{2} \cdot V_{POS}/\sqrt{2}}{(I_{MAX}/2) \cdot V_{POS}} = 50 \%$$

Class B:  $\frac{P_{1}}{P_{dc}} = \frac{(I_{MAX}/2)/\sqrt{2} \cdot V_{POS}/\sqrt{2}}{(I_{MAX}/\pi) \cdot V_{POS}} = 78 \%$

**Class C:** Ideally can go to 100%, but P<sub>1</sub> drops steadily beyond  $\alpha = \pi$ , goes to 0 at 100%!

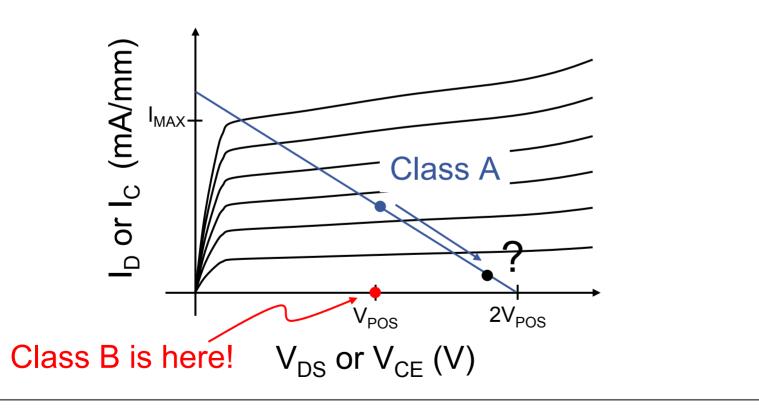

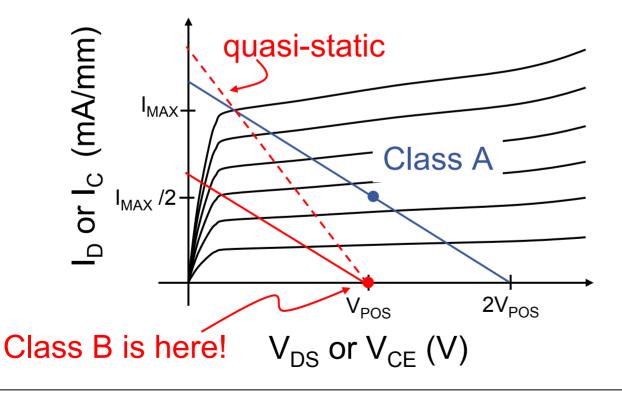

#### What happened to our load line?

For class B fundamental R<sub>L,opt</sub> = V<sub>POS</sub>/(I<sub>MAX</sub>/2) – Didn't change

#### What happened to our load line?

For class B fundamental R<sub>L,opt</sub> = V<sub>POS</sub>/(I<sub>MAX</sub>/2) – Didn't change

In quasi-static picture, resistance presented to transistor output cut in half. But average resistance is the same for class A

- Now consider "linearity"

- Clearly the current waveforms are far from linear

BUT ...

Overall P<sub>OUT</sub> vs. P<sub>IN</sub> transfer function can still be quite linear, especially for true Class B where output current waveform is symmetrical with respect to input waveform

Because conduction angle is constant,  $\mathsf{P}_{\mathsf{OUT}}$  changes proportional to  $\mathsf{P}_{\mathsf{IN}}$

- IDEAL: Design each stage independently

- Determine required gain number of stages

- Determine P<sub>OUT</sub> for each stage

- Determine R<sub>L,opt</sub> for each stage

- Determine input impedance for each stage

- Design matching networks for inter-stage, load and input

- REALITY:

- I<sub>MAX</sub> doesn't scale nicely with transistor size. Without good I<sub>MAX</sub> numbers, can't determine R<sub>L,opt</sub>. Need to do load-pull.

- Even load pull measurements have limited accuracy for very large transistors

- Designs are very empirically driven!

RF 🖁 IF

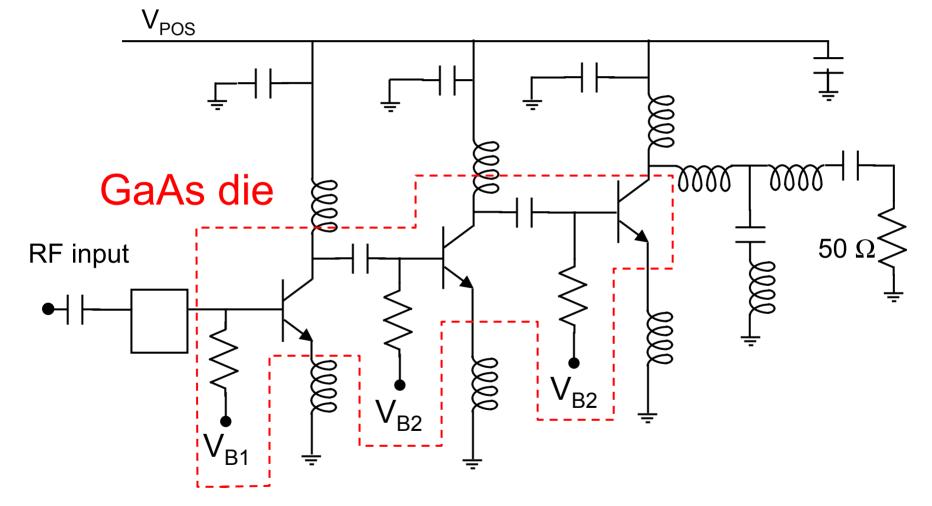

## GSM 900 MHz, GaAs HBT PA Design

#### **3 STAGE DESIGN**

my m

RFAIF

• Stage 1: Gain = 10 dB  $\rightarrow$  P<sub>OUT</sub> = 15 dBm • R<sub>L1</sub> = V<sub>CC</sub><sup>2</sup> / 2\*P<sub>OUT</sub> = 194  $\Omega$ • I<sub>MAX</sub> = 2\*V<sub>CC</sub> /R<sub>LOAD</sub> = 36 mA • Chose class A: I<sub>DC</sub> = I<sub>MAX</sub>/2 = 18 mA (18 mA insignificant compared to 2.33 A) • Stage 2: Gain = 10 dB  $\rightarrow$  P<sub>OUT</sub> = 25 dBm • R<sub>L2</sub> = 19.4  $\Omega$ • I<sub>MAX</sub> = 360 mA

- Still probably class A (maybe AB): I<sub>DC</sub> = I<sub>MAX</sub>/2 = 180 mA

- Stage 3: Gain = 7 dB  $\rightarrow$  P<sub>OUT</sub> = 33 dBm

• Class B:

$$I_{DC} = I_{MAX}/\pi = 742 \text{ mA}$$

RFAIF

## A note on "Gain"

• Taking a very simplistic view of common emitter stages:

- $g_{m1} = I_C / V_{Th} = 18 \text{ mA} / 0.025 \text{ V} = 0.696 \text{ S}$

- $g_{m1}R_{L1} = 0.696 \cdot 194 = 135 \rightarrow NOT 10 dB!$

BUT ...

my have

RF IF

- $r_{e1} = 1/g_{m1} = 1.44 \Omega$

- $r_{e2} = 1/g_{m2} = 0.144 \Omega$

- $r_{e3} = 1/g_{m3} = 0.035 \Omega$

- 1. Remember it's power gain, not voltage gain. Can lose voltage at input match.

- 2. It's pretty tough not to get significant degeneration!

#### • Efficiency calculations:

- $I_{DC1}$  = 18 mA,  $I_{DC2}$  = 180 mA,  $I_{DC3}$  = 742 mA

- Total DC Current: 940 mA

$$\frac{P_{I}}{P_{dc}} = \frac{(I_{MAX}/2)/\sqrt{2} \cdot V_{POS}/\sqrt{2}}{I_{DC} \cdot V_{POS}} = 62\%$$

Realistically may get as high as 55%

my have

#### **Real-World Design Example: Load-Pull**

After initial "guesses" at transistor sizes, load-pull to determine actual target load for matching circuits

RF 🖁 IF

## **Real-World Design Example: Load-pull**

# Notes on load-pulling:

- Most accurate on probe station, but insertion loss of probes prevents it from being useful for large transistors

- ("Insertion loss" is RF code word for resistance)

- Bonded devices on evaluation board must be carefully deembedded

- Even using electronic tuners, accuracy is poor for very large transistor (i.e. for loads in the 2 – 5 Ω range)

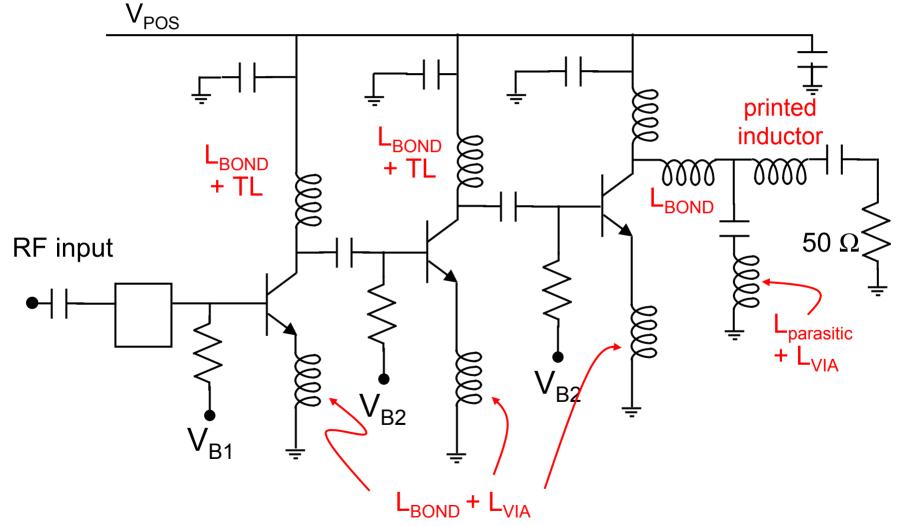

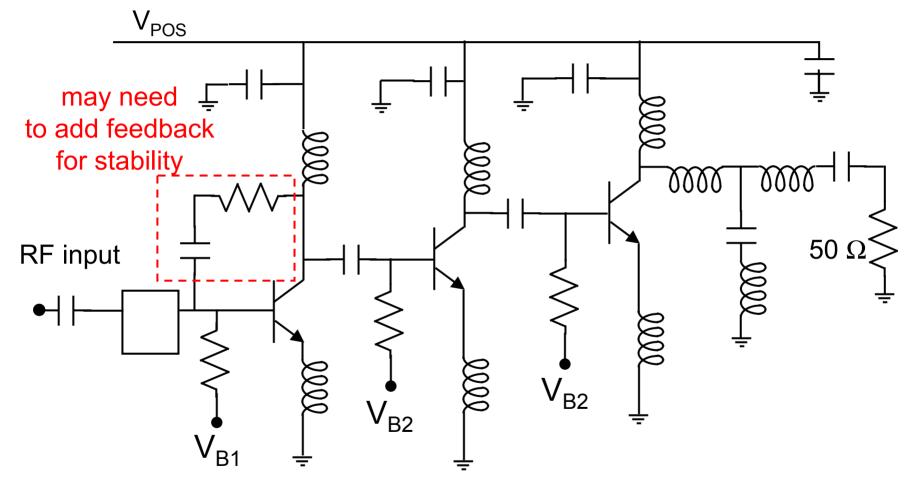

# **Real-World Design Example: The Circuit**

#### **Real-World Design Example: The Circuit**

#### **Real-World Design Example**

#### **Real-World Design Example**

# **Real-World Design Example: Tuning**

# **Real-World Design Example: Tuning**

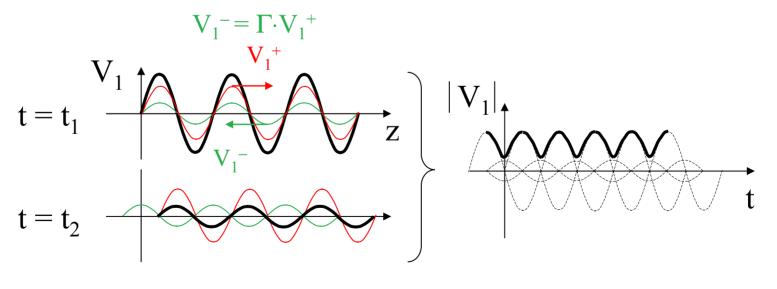

#### Ruggedness

- 50  $\Omega$  load is for antenna in free space. Place antenna on a metal plate and can easily get VSWR of 4:1

- Typical PA specs are: don't oscillate at up to 4:1, survive up to 10:1 (!)

- Linearity

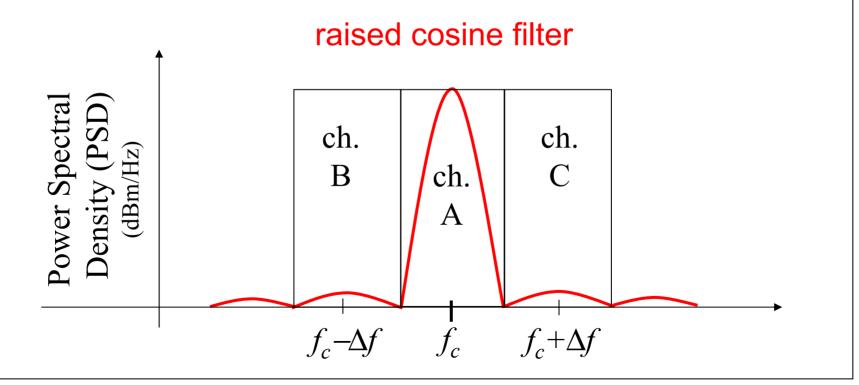

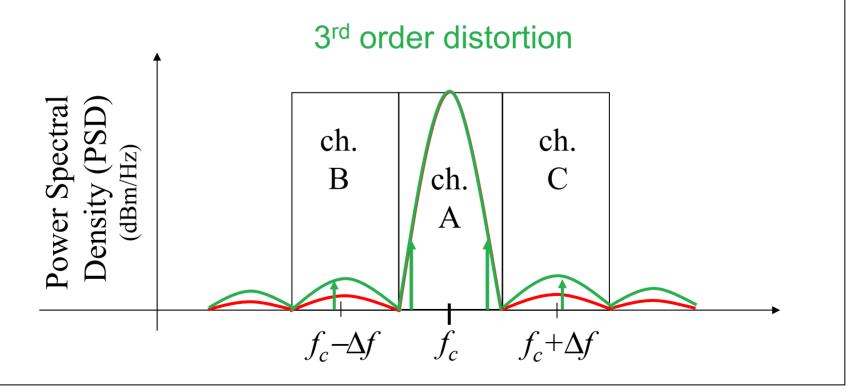

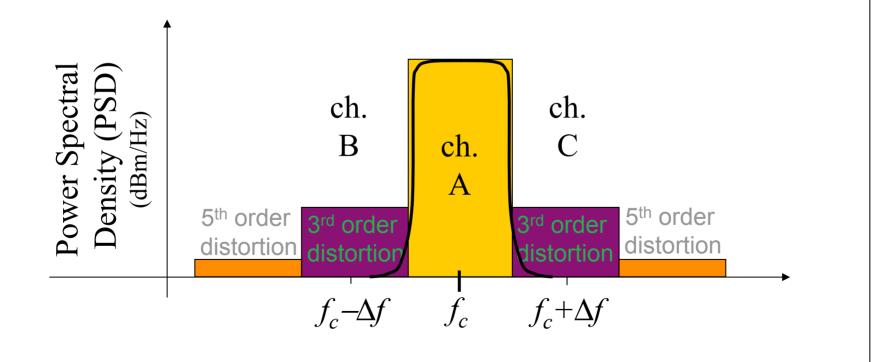

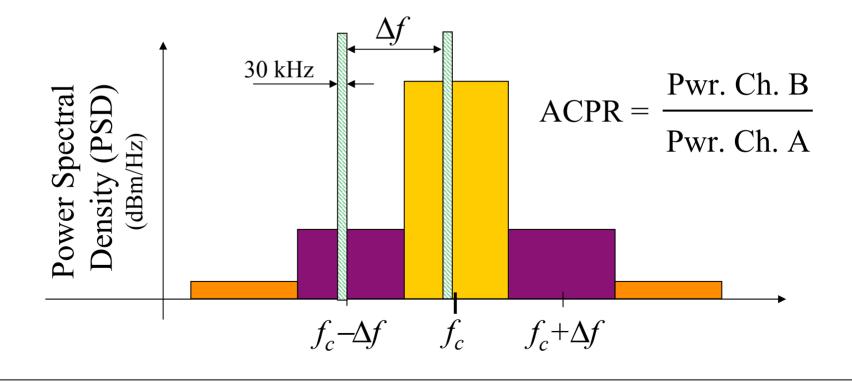

- For linear PAs, Adjacent Channel Power Ratio (ACPR) is very important

- Linearity

- For linear PAs, Adjacent Channel Power Ratio (ACPR) is very important

- Linearity

- For linear PAs, Adjacent Channel Power Ratio (ACPR) is very important

- Linearity

- For linear PAs, Adjacent Channel Power Ratio (ACPR) is very important

- Linearity

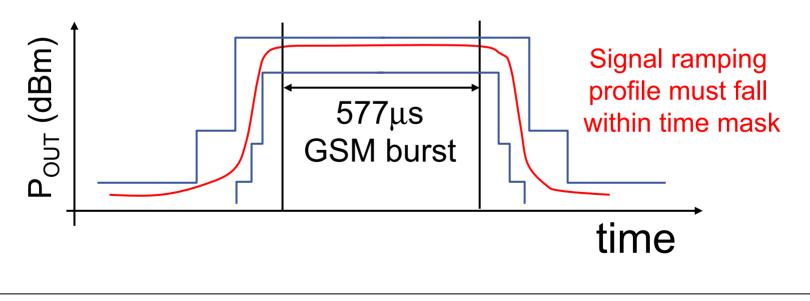

- For non-linear PA in TDMA systems, harmonic spurs and switching transients are most common measure of linearity

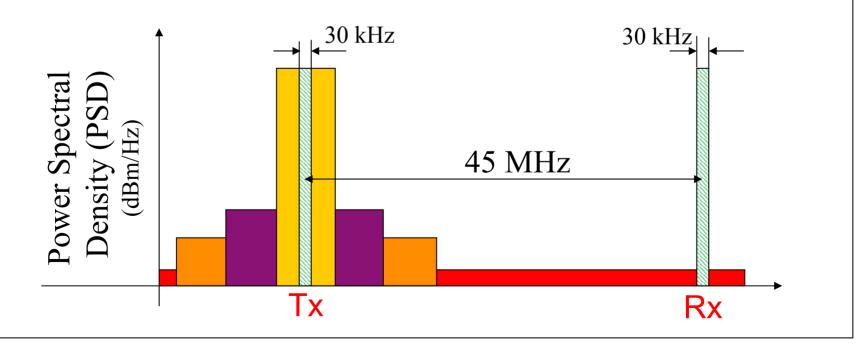

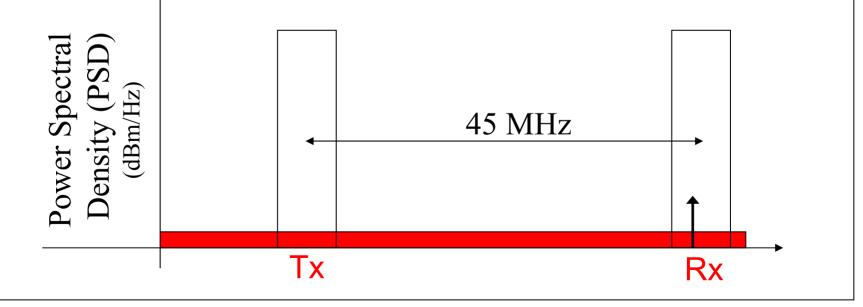

- Noise in receive band:

- Obvious spec. in systems where Tx and Rx are operating at the same time (FDD)

- Noise in receive band:

- Obvious spec. in systems where Tx and Rx are operating at the same time (FDD)

- Not so obvious spec in TDD system. Problem primarily of mixing by the PA ( $2\omega_2 \omega_1$  or  $\omega_2 \omega_1$ )

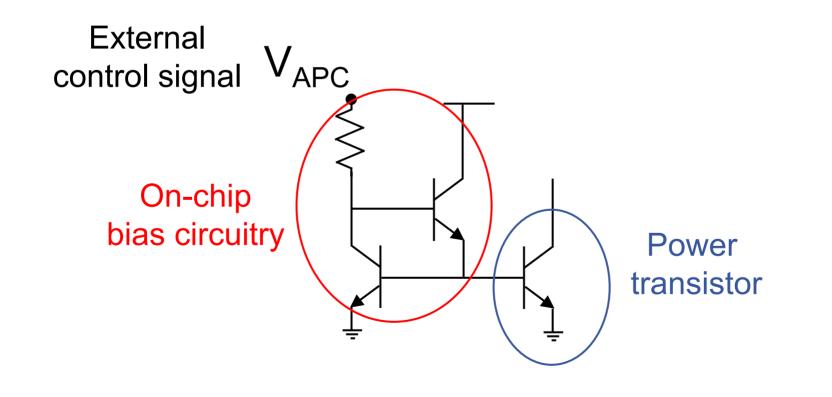

#### **Power Control**

- For linear PA, expected to operate at constant gain. Power control is therefore a function of P<sub>IN</sub>.

- Role of bias circuitry is to maintain constant gain over P<sub>IN</sub>, temperature (PTAT?).

## **Power Control**

For non-linear PA, expected to operate at constant P<sub>IN</sub>.

Power control is achieved by varying gain.